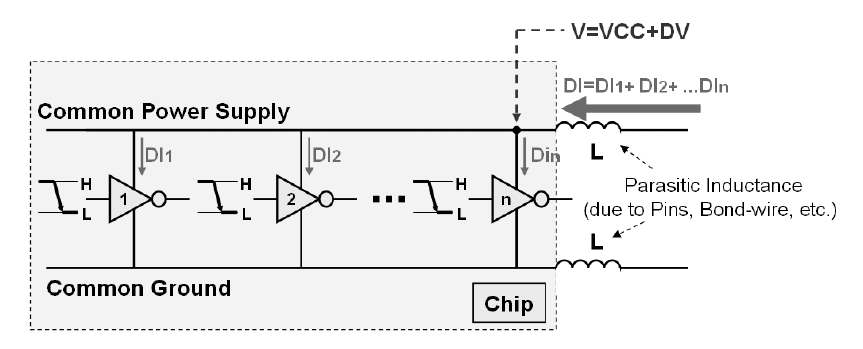

Synchronous switching noise

Synchronous switching noise is defined as when multiple I/O ports of the chip are flipped in the same direction at the same time, such as from 1 to 0, the current consumed by multiple I/O buffers at the same time is superimposed on the power supply and ground pins to generate a larger current, and this changing current will form a noise voltage dV=L*dI/dt on the parasitic inductance L of the package and pins, which is synchronous switching voltage noise.

Synchronous switching noise voltage generation schematic

- Created Date: 2025-03-13 15:29:24 ;

- Last modified on 2025-03-13 15:29:24 ;