IC 集成电路芯片受ESD静电的影响评价

- 文章目录: 集成电路电磁兼容如何测试

简介:

如今,电子制造的新发展越来越受到 EMC 要求的支配。由于电子模块在EMC符合性测试中失败,导致产品开发的后续成本相当可观。电子系统中使用的集成电路对其整体 EMC 性能起决定性作用。IC 通常是造成干扰发射或抗扰弱点的原因,在这种情况下很难控制它们。

随着时间的推移,IC 的结构变得越来越小,这导致更高的开关速率并需要降低电源电压。由于这两个因素,IC 变得更容易受到 ESD 的影响。

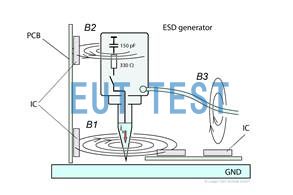

图 1 使用 ESD 枪注入被测设备的电流脉冲。

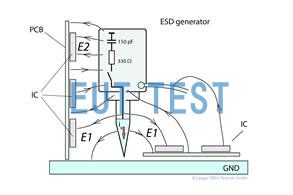

图 2 一个磁和一个电干扰场被感应。

使用ESD静电枪注入被测IC

在根据 IEC 64000-4-2 标准进行的 EMC 一致性测试中,使用 ESD 发生器(ESD 枪)测试电子设备。ESD发生器产生标准要求的电流脉冲(图3),注入被测器件(图1))。该 ESD 脉冲耦合到电子设备的金属部件中,并从那里通过导电和电容/电感耦合移动到 IC。干扰脉冲的幅度在其到达 IC 的路径上随时间变化。本报告的目的是研究 IC 的耦合路径。影响 IC 的干扰脉冲的幅度被测量为各个耦合路径的时间函数。这有助于确定哪些耦合是相关的,哪些参数(上升时间、电压强度、波形、幅度、电流、电压、电场或磁场)对耦合有影响。这些发现允许开发选定的 EMC 对策来保护 IC。

ESD 发生器感应出了磁场和电场干扰:

除了符合标准的电流脉冲外,ESD 发生器还会感应磁场和电场(图 1、图 2)。由于放电电流,在 ESD 发生器的尖端会产生一个磁涡流场,该涡旋场在 IC 和模块的线路网络中旋转。在磁场穿透的导体回路中会感应出干扰电压。该电压叠加在电子系统的电信号上并导致电子设备出现故障。

电感器集成在 ESD 发生器的尖端。来自 ESD 枪的放电电流会导致该电感器上出现电压降。这个电压降会产生一个电场 E1,它从发生器的尖端出现并通过线路和 IC 延伸到被测设备中(图 2)。因此,干扰电流脉冲被传输到线路和 IC 中,导致电子设备出现故障。

除了标准中描述的通过其尖端发出的干扰电流外,ESD发生器的主体中还出现了电场和磁场(图1,图2))。如果作为时间的函数进行比较,这些场和标准所描述的干扰事件可能完全不同。这些场对电子设备具有额外的干扰影响,其可能超过由尖端干扰引起的期望影响。这些场对电子设备的干扰程度取决于 ESD 发生器相对于设备模块的位置。当 ESD 发生器被转动和倾斜时,设备中的弱点可能纯粹是偶然地响应。电子设备的功能故障似乎以一种混乱的方式发生。开发人员无法再理解和分析因果关系。

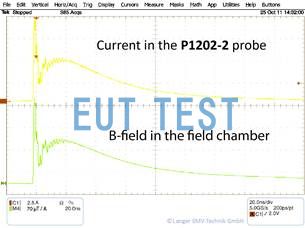

图 3 由 ESD 发生器触发的干扰的电流随时间变化(顶部)

ESD 发生器尖端附近的磁通密度(底部)

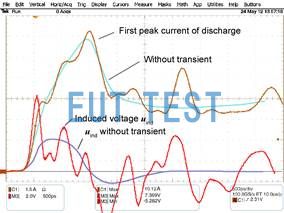

图4 模块

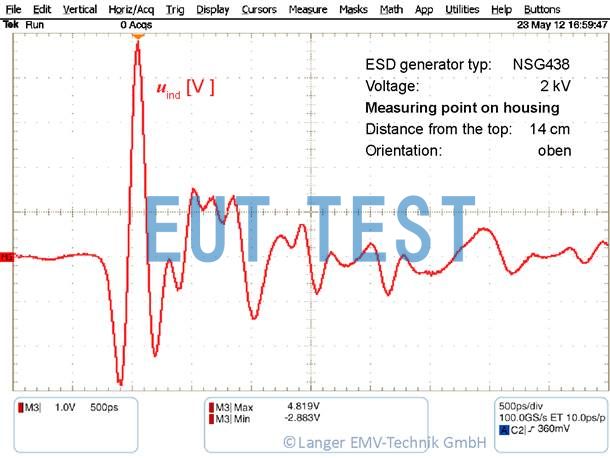

ESD枪电流回路中ESD发生器第一次放电峰值电流感应电压und :NSG435

电压:2 kV

图 4以放大的形式显示了 ESD 发生器的第一个放电峰值电流。几个瞬变在前沿上清晰可见,在下文中被指定为 ESD 瞬变。放电电流峰值和 ESD 瞬变也会产生随时间变化相同的磁通量 B1(图 1)。磁通量 B1在电子模块的导体回路中感应出干扰电压 uind(图 4)。导体回路的尺寸为 8 mm2。ESD 发生器的电压设置为 2 kV。此外,图 4清楚地表明最大的电压感应是由 ESD 瞬态产生的。标准定义的 0.7 至 1 ns 放电电流峰值的上升时间会产生较低的干扰电压感应(图 4,没有瞬态的曲线)。

ESD 发生器的 ESD 瞬态比放电电流峰值具有更强的干扰效应。因此,标准定义的波形参数不适合全面描述ESD发生器的扰动效应。瞬态在很大程度上取决于实践中使用的 ESD 发生器的类型。

场 B2 和 B3 增强了 ESD 发生器的干扰效应(图 1)。图 5显示了由磁场 B2 在 8 mm2 的导体回路中感应出的干扰电压。电压随时间的变化与通常已知的 ESD 事件的通常曲线完全不同。200 ps 宽的尖峰对 IC 的干扰影响最大。它的振幅为 4.8 V。这个脉冲对于较慢的老一代 IC 来说太短了,几乎不会造成任何问题。现代、快速的 IC 可以处理这种窄脉冲,并且会出现故障。这个事件的特殊之处,即场B2感应的电压,是它与标准脉冲无关。它发生在实际测试之外,这意味着标准测试不再是明确的。

图 5由 ESD 发生器外壳产生的场 B2 在 8 mm2 的导体回路中感应出的电压。

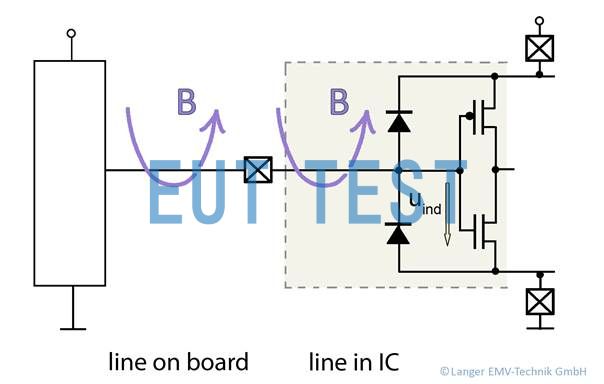

图 6显示了通过 ESD 发生器的磁场 B 产生电压感应(等效电路)背后的工作原理。感应回路可以位于印刷电路板上的 IC 外部或 IC 封装内部。在此示例中,它在外部由通过低阻抗驱动器接地的走线形成。干扰电压通过导电耦合通过迹线进入 IC。在 IC 内部,感应回路由引脚、引线框架和键合线构成。感应回路中感应的电压 uin 出现在 IC 输入端。内部电压和外部电压都会导致 IC 内部出现故障。电压 uind 分别取决于 ESD 发生器的放电电流和磁场的变化率。这种相关性由归纳定律描述: uind = -d Φ / d t。扰动的变化率越快,感应电压越高。符合 IEC 64000-4-4 的突发发生器提供上升时间为 5 ns 的脉冲。脉冲串发生器的磁场感应出的电压低于 ESD 发生器产生的干扰电压。ESD 发生器提供上升时间为 0.7 到 1 ns 的脉冲,并在相同的电流值下感应出高出五倍的电压。ESD 发生器的前沿瞬变的上升时间约为 200 秒。这些瞬变会引起更高的电压。

图 6 ESD 枪的磁场在电子模块或 IC 的导体回路上感应出的电压。

图 7显示了这种相关性。此处显示的电流会产生穿过导体回路的磁场 B。电压 uid 在导体回路中感应。干扰事件:突发、ESD、ESD 瞬变会引起不同的电压。感应电压脉冲的宽度对应于电流的变化率。突发事件期间会产生宽度为 5 ns 的脉冲。ESD 事件产生宽度为 1 ns 的脉冲,ESD 瞬变产生宽度为 200 ps 的脉冲。现代 IC 还将处理宽度为 200 ps 的脉冲,这将导致 IC 故障甚至完全失效。

图 7干扰事件期间8 mm 2导体回路中感应的电压:突发、ESD、ESD 瞬变

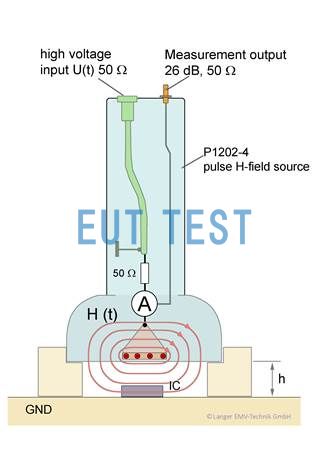

图 8 确定 IC 抗磁场干扰的测试装置

根据感应定律,感应电压的值与扰动事件的变化率成反比。图 7的测量是使用定义的场源进行的(图 8)。这些场源对于不同的干扰具有固定的场生成几何形状。因此,测试电流将始终产生相同的场耦合,以便可以比较针对所描述的三个干扰事件的测量结果。IC 可以经受定义的场及其在操作中的抗扰度测试。

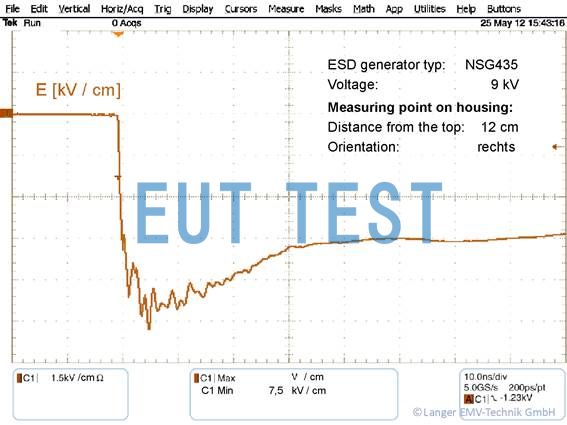

在放电过程中,ESD 发生器中的高压开关、电流导体和其他组件处会出现变化率很高的开关电压(图 2)。这些开关电压产生的电场变化率很高,从发电机外壳耦合到被测设备。图 9显示了从 ESD 发生器外壳后部产生的电场。它的变化率约为。1 纳秒。

图 9 NSG435 ESD 发生器后部的电场,电压为 9 kV。

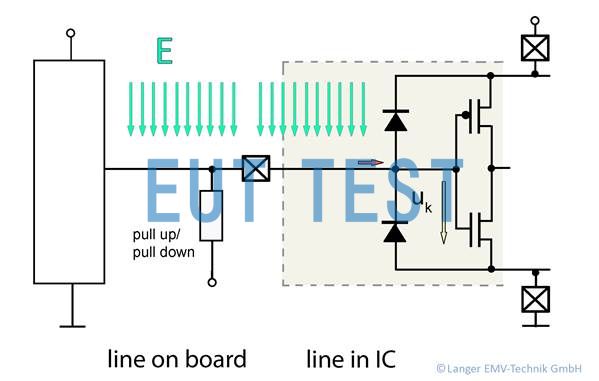

图 10显示了等效电路图和ESD发生器电场耦合背后的工作原理。电场耦合到信号线中。受影响的信号线和 ESD 发生器之间的电容耦合很低。该电容的值取决于信号线的表面积,并且在这种耦合的 fF 范围内。ESD 发生器的电场驱动电容电流进入信号线。该电流通过上拉电阻或所连接驱动器的内部电阻流到地 (GND)。电流在电阻器上产生电压脉冲。该电压脉冲到达 IC 的输入端并干扰 IC。电压脉冲的峰值取决于电场的变化率,上拉电阻和信号线受电场作用的表面积。脉冲宽度取决于上升时间。扰动的变化率越快,耦合输入的电压就越高。符合 IEC 64000-4-4 的脉冲发生器提供上升时间为 5 ns 的脉冲。突发事件的电场耦合的电压低于由 ESD 发生器触发的干扰。ESD 发生器提供上升时间为 0.7 到 1 ns 的脉冲,并将高五倍的电压耦合到被测器件中。来自 ESD 发生器的 E 场的最高变化率约为 200 秒。由于这些事件,更高的电压被耦合到被测设备中。耦合输入的电压越高。符合 IEC 64000-4-4 的突发发生器提供上升时间为 5 ns 的脉冲。突发事件的电场耦合的电压低于由 ESD 发生器触发的干扰。ESD 发生器提供上升时间为 0.7 到 1 ns 的脉冲,并将高五倍的电压耦合到被测器件中。来自 ESD 发生器的 E 场的最高变化率约为 200 秒。由于这些事件,更高的电压被耦合到被测设备中。耦合输入的电压越高。符合 IEC 64000-4-4 的突发发生器提供上升时间为 5 ns 的脉冲。突发事件的电场耦合的电压低于由 ESD 发生器触发的干扰。ESD 发生器提供上升时间为 0.7 到 1 ns 的脉冲,并将高五倍的电压耦合到被测器件中。来自 ESD 发生器的 E 场的最高变化率约为 200 秒。由于这些事件,更高的电压被耦合到被测设备中。7 到 1 ns 并将高五倍的电压耦合到被测器件中。来自 ESD 发生器的 E 场的最高变化率约为 200 秒。由于这些事件,更高的电压被耦合到被测设备中。7 到 1 ns 并将高五倍的电压耦合到被测器件中。来自 ESD 发生器的 E 场的最高变化率约为 200 秒。由于这些事件,更高的电压被耦合到被测设备中。

图 10 将 E 场耦合到电子模块或 IC 的导体中

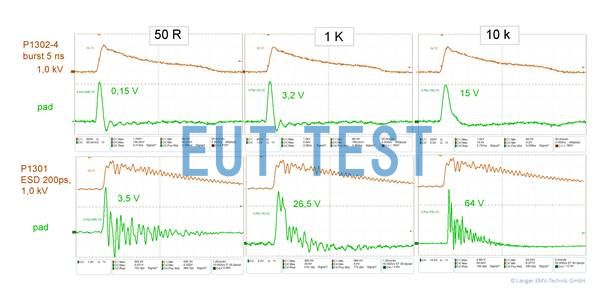

在实验中研究了这种电耦合。这些实验使用了如图 8所示的类似测试设置。E 字段源用于生成所需字段。图 11显示了结果。5 ns 突发脉冲和 200 ps ESD 脉冲用于测量。此外,还检查了对设置中使用的上拉电阻(驱动器)的依赖性。

耦合到 IC 的电压与上拉电阻成正比。最低电压 (0.15 V) 以 5 ns 的变化率和 50 欧姆的上拉电阻耦合到 IC。该电压还不会干扰 IC。最高电压以 200 ps 的变化率和 10 kOhm 的上拉电阻产生,达到 64 V。图 11显示 200 ps 脉冲已经可以导致 IC 出现故障,该 IC 具有 50 欧姆的低阻抗上拉(驱动器)电阻(电压为 3.5 V)。这使得该脉冲对电子电路特别危险,因为即使是由低阻抗源(例如数据总线、地址总线等)驱动的最小线路部分也可能成为这种方式的干扰的受害者。相应线路上测试焊盘大小的表面积足以导致 IC 出现故障。这个问题仅限于现代、高度集成的 IC,它们的速度足以处理这种类型的脉冲。

图 11 作为干扰脉冲上升时间和电路中使用的上拉电阻值的函数,到导体的电耦合。

对于设计人员来说,了解计划用于具有高度集成电路的模块的 IC 的抗扰度非常重要。并非 IC 的所有引脚对 EMI 都同样敏感。通常只有几个高度敏感的引脚。必须识别这些引脚,以便采取适当和有效的 EMC 对策。

例如,信号线应在内层走线,并通过两侧的 GND 平面进行屏蔽,以减少电场的干扰影响。必须注意的是,测试焊盘和通孔的数量也必须减少。

现代测量技术和测试设备可用于确定 IC 的传导和辐射抗扰度。

- 创建日期: 2024-08-26 10:35:11 ;

- 最后修改日期: 2024-08-26 18:35:11 ;