IC 集成电路芯片受电磁场耦合引起的反应

- 文章目录: 集成电路电磁兼容如何测试

简介:

EMC对芯片功能的影响可能会有很大差异,从短暂的可容忍故障(例如端口输出的短时间切换)到 IC 的完全故障,即功能的永久性丧失。

本文讨论通过 IC 引脚进行的传导干扰。在这些情况下,干扰会通过电子板的线路网络进入 IC。源自电子板环境的电磁脉冲和 ESD 场是造成这些传导干扰的原因。

ESD和突发如何在电子系统中产生电磁干扰?

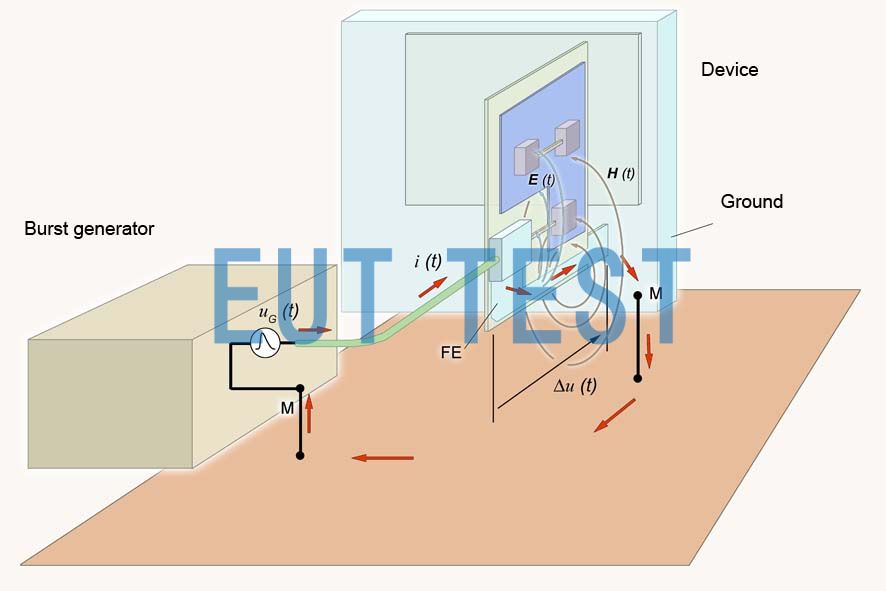

在 EMC 测试期间注入电子设备的干扰会产生磁场和电干扰场。这些场穿透电子板(图 1)。

图 1突发或 ESD 干扰对电子板的影响。

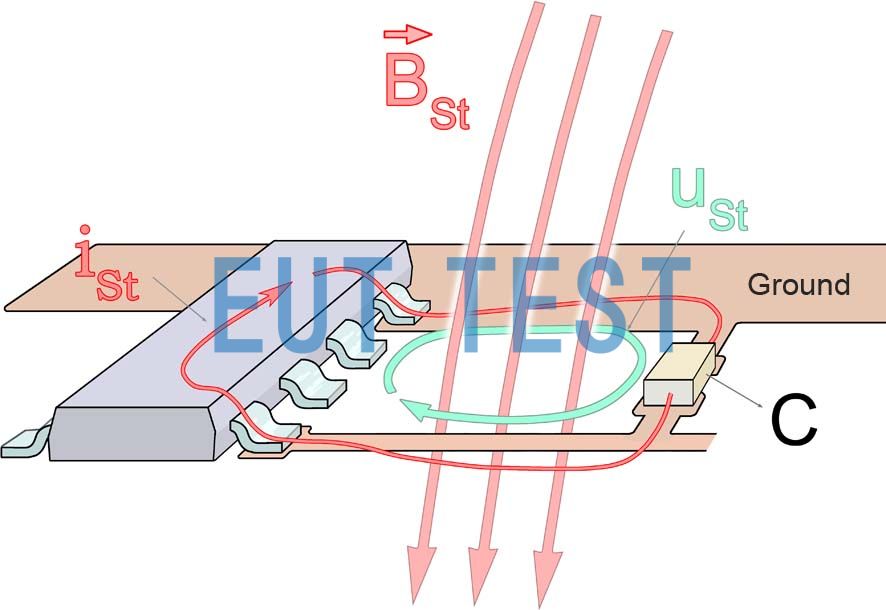

电感耦合(B/H 场)

电子板的线路相对于地平面形成环路。如果磁场现在进入这些环路,就会在其中感应出对地电压。如果导体回路连接到 IC 引脚,则该引脚上会存在接地感应电压(图 2)。感应电压可能会干扰信号线上的有用信号,并将干扰电流驱动到 IC 中。

电感耦合具有低源阻抗并驱动高强度电流进入 IC。电流值在高达 30 A 的范围内。为了使低源阻抗有效,线路必须以低电阻(电容器)连接到 IC 外部的地。

图 2通过磁场干扰电子板上的线路网络。

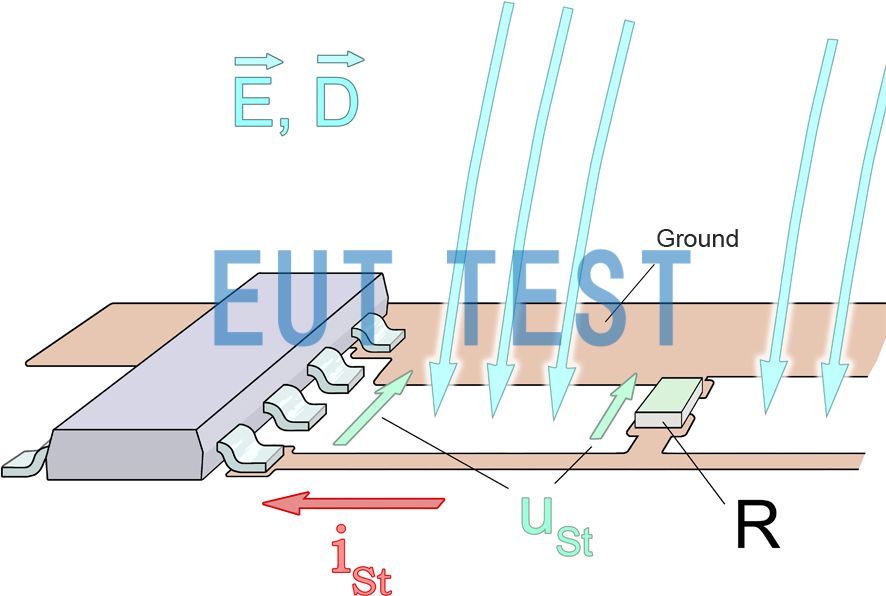

电容耦合(电场)

电路板上的线路形成干扰电场的耦合电极,如图 1 所示。电场将干扰电流耦合到线路(耦合电极)。干扰电流通过上拉、下拉或驱动器流向地,并在它们两端产生干扰电压降(图 2)。感应干扰电压存在于 IC 输入端,可以修改有用信号或将干扰电流驱动到 IC 中。电容耦合具有高源阻抗并驱动低强度电流进入 IC。电流强度在高达 1 A 的范围内。为了使高源阻抗有效,线路必须通过高电阻(电阻器 R)上的上拉、下拉连接到 IC 外部的地。

图 3通过电场干扰电子板上的线路网络。

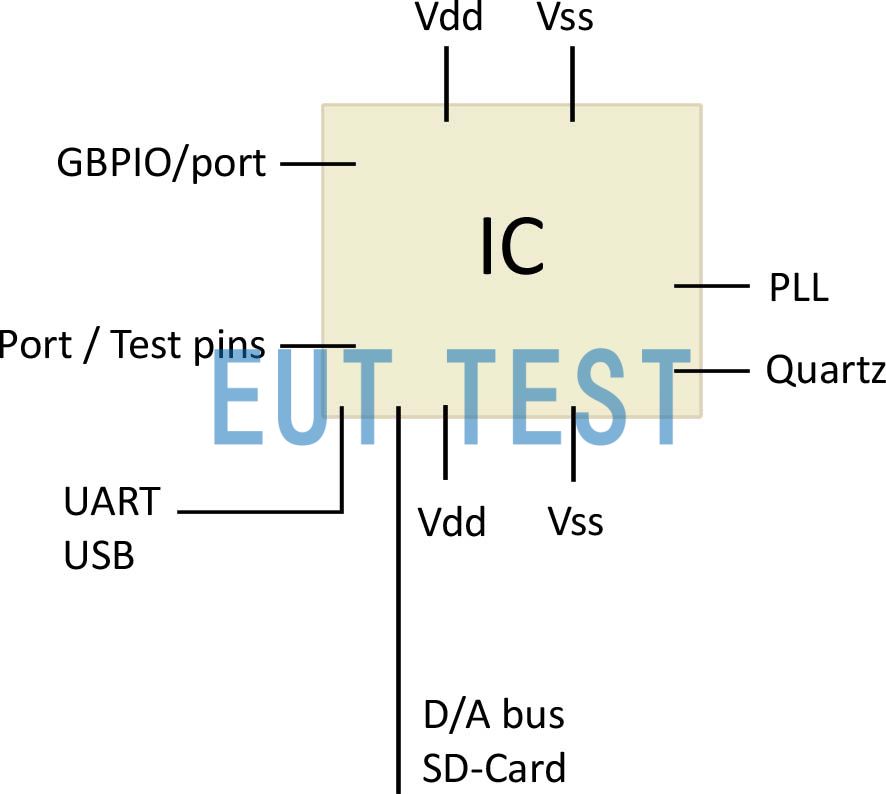

具有针对传导干扰的 EMC 特性的 IC 引脚

图 4 IC 引脚及其各自的 EMC 特性。

由于电容或电感耦合机制,传导干扰通过其引脚进入 IC。耦合机制的特性以及连接到 IC 引脚的 IC 电子器件的各自特性决定了某些因果关系。根据连接的 IC 电子设备的 EMC 特性,IC 引脚可以分为几个引脚组。

最重要的信号引脚组是:

- 端口引脚

- 测试引脚

- 接口(USB、UART 等)

- 总线引脚

- 晶振连接引脚

- 复位引脚

- 电源引脚:Vdd 和 Vss 引脚

信号引脚 – IC 对电场耦合引起的干扰的反应

第一种可能的反应:

由于与电子板信号线的电容耦合,干扰电压叠加在有用信号上。干扰电压改变有用信号的逻辑状态。当微控制器读取有用信号时,可能出现以下反应:

- 通过在微控制器中进行多次扫描来检查有用信号是否存在可能的干扰。根据这个原理可以滤除杂散脉冲。

- 如果测试引脚没有正确锁定,虚假信号会将微控制器切换到测试模式,这反过来会导致微控制器完全失效。

- 接口具有错误检测和纠正机制,可以检测和纠正有用信号逻辑状态的变化。

- 如果有用信号是总线信号,则通常没有防止杂散脉冲的保护。错误的数据、地址或控制信号被读取并可能导致微控制器崩溃。

- 晶振连接引脚

- 耦合到晶体振荡器连接引脚的干扰可能会导致晶体振荡器和 PLL 电路发生故障。1 .

- 如果有用信号是复位信号,则在微控制器中布置滤波器以消除干扰。如果过滤器的尺寸不合适,干扰将能够通过过滤器。

第二种可能的反应:

耦合进来的干扰电压上升到保护二极管的极限电压并打开它们。因此,干扰电流通过保护二极管流入 IC 的 Vdd 和 Vss 网络。干扰电流使 Vdd 和 Vss 之间的内部电容反向。如果电流沿负方向流动,内部电容将放电并导致电源电压骤降。这是从外面看不到的。微控制器失去其逻辑寄存器状态并崩溃。此外,干扰电流会在 Vdd、Vss 系统的串联电感两端产生干扰电压。这些干扰电压会在 IC 的不同逻辑区域(杂项、存储器、PLL)之间造成干扰,由此产生的电压差异会干扰逻辑区域之间的信号交换。

如果电路布局不利,集成在 Vdd 和 Vss 中的 ESD 保护二极管也可能响应这种干扰(电源钳位)并使 IC 短路。这可能会导致 IC 故障甚至毁坏。

IC 对磁场耦合引起的干扰的反应:

由于与电子板的信号线的电感耦合,干扰电压叠加在有用信号上。只有当电子板上的信号线以低电阻接地时,耦合才有效。确保这一点的最佳方法是通过滤波电容器将信号线接地。驱动器的电阻通常低到足以引起磁场干扰。这些先决条件允许磁场驱动比电场强度高得多的干扰电流进入 IC。功率钳的效果特别强。根据 IC 内部的阻抗关系,磁场的影响可能比电场的弱或强。

电源引脚

如果磁场耦合到电子板的电源网络,干扰通常只能进入电源引脚。

磁场将干扰电流驱动到 IC 的 Vdd / Vss 回路中。干扰电流使 Vdd 和 Vss 之间的内部电容反向。如果电流沿负方向流动,内部电容将放电并导致电源电压骤降。这是从外面看不到的。微控制器失去其逻辑寄存器状态并崩溃。此外,干扰电流会在 Vdd、Vss 系统的串联电感两端产生干扰电压。这些干扰电压会在 IC 的不同逻辑区域(杂项、存储器、PLL)之间造成干扰,由此产生的电压差异会干扰逻辑区域之间的信号交换。与由于电场而通过保护二极管进入 IC 的干扰电流相比,干扰效应更为强烈。

通过磁场耦合到 Vdd/Vss 回路的干扰电流也会导致集成的 ESD 保护二极管做出响应(电源钳位)。如果电源钳位电路设计不当,可能会导致 IC 短路。这可能会导致 IC 故障甚至毁坏。

IC 环境的设计规则——电场/磁场耦合

以下设计规则在实践中已被证明成功地解决了上述问题。

电场

如果电子板到相邻接地区域的线路网络保持非常短或完全嵌入接地平面,则电场(ESD、突发)的影响会减弱或完全被阻止。这意味着线路应铺设在两个接地层之间。

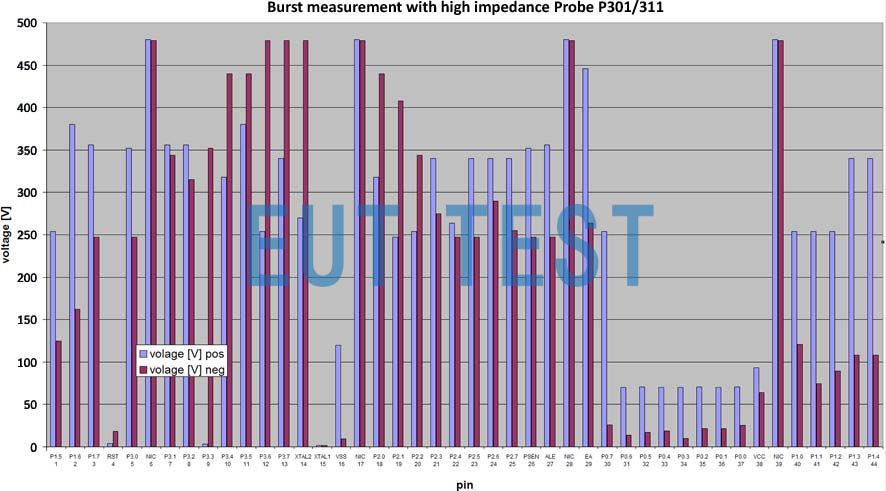

IC 引脚的灵敏度决定了线路网络必须被地屏蔽的程度。IC 引脚灵敏度是一个可以定义的值,因此也可以针对每个单独的引脚进行测量(图 5)。

图 5微控制器引脚对影响电子板线路网络的干扰的传导敏感性

图 5显示 IC 引脚灵敏度变化很大。如果引脚不敏感,则线路网络可能位于不受地平面保护的电子板表面,而不会因电场(图 5中 > 400 伏的电平)而产生任何干扰 。如果引脚很敏感,即使通过地平面对线路网络进行完全屏蔽,也可能仍然不够充分。测试点的表面或连接到线路网络的 IC 引脚的表面可能足以吸收来自电场的干扰电流。线路网络的表面积(只有几平方毫米)大到足以因电场引起 IC 干扰。微控制器的晶体振荡器连接可能具有如此高的灵敏度,例如(图 5水平约。1-2 伏)

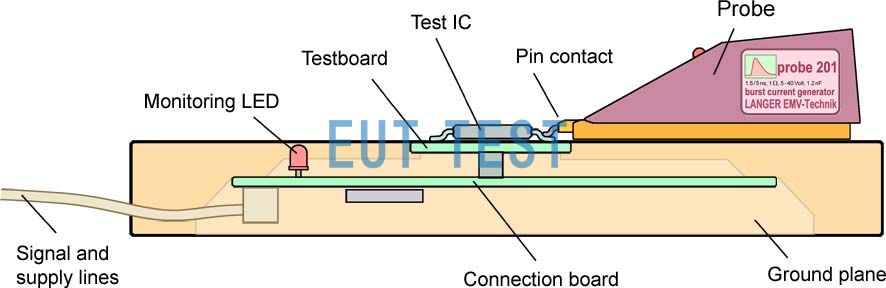

图 6显示了用于确定对传导干扰的灵敏度的测量设置。IC 引脚可以单独接触特殊探针并施加测试脉冲。该测试脉冲对应于电场(突发,ESD)对电子板线路网络的影响。

图 6用于确定引脚对电子板上电场引起的传导干扰的灵敏度的测量设置

磁场

IC 引脚对干扰电流脉冲(突发、ESD 磁场)的敏感性可以在类似于图 5的图表中显示 。与干扰相关的电流范围在 0.5 到 35 安培之间。如果引脚敏感,几平方毫米的感应回路就足以引起感应耦合。这些环路可以由距接地平面 0.5 毫米层距的短线段形成。阻塞电容器也可能形成关键回路,特别是如果布置在电子板的边缘。通常可以在那里找到最高的磁场强度,这会导致最高的电压感应。

如果电子板具有带槽的接地系统(分离接地),则磁场可能会进入并在跨线网络中感应出电压。如果模拟地平面和数字地平面分开,这通常会发生。只有地平面不分离并连续连接才能解决该问题。晶体振荡器和 PLL 电路的电源引脚是实际中最敏感的引脚。IC 的信号连接,例如复位、晶体振荡器或测试引脚,也可能非常敏感。

在电子板开发的早期阶段,将布局设计和机械结构与 IC 引脚灵敏度相匹配是有益的。这增加了电子板的 EMC 抗扰度。今天,IC 制造商已经测量了 IC 引脚的传导灵敏度。

- 创建日期: 2024-08-26 10:38:25 ;

- 最后修改日期: 2024-08-26 18:38:25 ;