从器件到芯片的EMC测试分析

- 文章目录: 集成电路电磁兼容如何测试

从器件到芯片的EMC测试分析-第 1 部分

介绍

符合 EMC 要求的要求越来越高。虽然技术进步允许缩小特征尺寸,但这也导致了控制设备抗扰度的特殊挑战。

这些增加的关于抗扰度的要求为设备的开发和制造增加了大量成本。然而,通过在组件级别(即 ASIC 和 IC)测试抗扰度,可以更容易地识别和采取对策。这些抗扰度测试结果允许预先选择特定的 IC 和 ASIC,以进行进一步的模块开发。此外,它们可以纳入 IC 和 ASIC 开发并有助于组件优化。

虽然业界已经有测试程序在评估 IC 和 ASIC 抗扰度方面提供了丰富的经验,但当前测试方法背后的概念是将干扰脉冲直接施加到测试 IC 的引脚上。所施加干扰的形状和幅度经过专门选择,以模拟当 IC 所在的设备经过标准化抗扰度测试或处于受干扰环境时 IC 将受到的典型干扰。

在运行过程中,技术设备、设施和装置一般由脉冲干扰信号供电。因此,标准设备测试模拟例如开关触点处的火花产生(爆发)或静电放电(ESD)。

使用标准测试方法,可以观察有源模式下的抗扰度(即正常工作的电压供电 IC 的行为)。通过测试的标准是功能不受干扰。

环境影响或测试本身可能导致电压和电流明显高于 IC 的规定最大值。

然而,在 IC 级分析抗扰度的好处是不需要考虑设备设计对 EMC 的影响。例如,这包括印刷电路板的设计、连接器的性质和可用性或外壳结构。

此外,在测试 IC 抗扰度时,干扰效应不如测试 [整个] 设备时那么明显。这使得测试结果具有更好的再现性。本文档描述了器件测试和IC 引脚测试之间的联系。

设备测试

由于电子产品的数字化程度不断提高和广泛使用,对设备抗扰度的鲁棒性要求很高,因此在测试技术设施和设备时,进行脉冲状干扰的抗扰度测试就显得尤为重要。这是因为它们在运行和标准使用过程中也会受到脉冲状干扰。

以下标准描述了抗扰度测试的相关干扰脉冲(突发和 ESD):IEC 61000-4-4 快速瞬态抗扰度测试(突发)和 IEC 61000-4-2 静电放电抗扰度(ESD):

| IEC 61000-4-4 | 快速瞬态抗扰度测试(突发) |

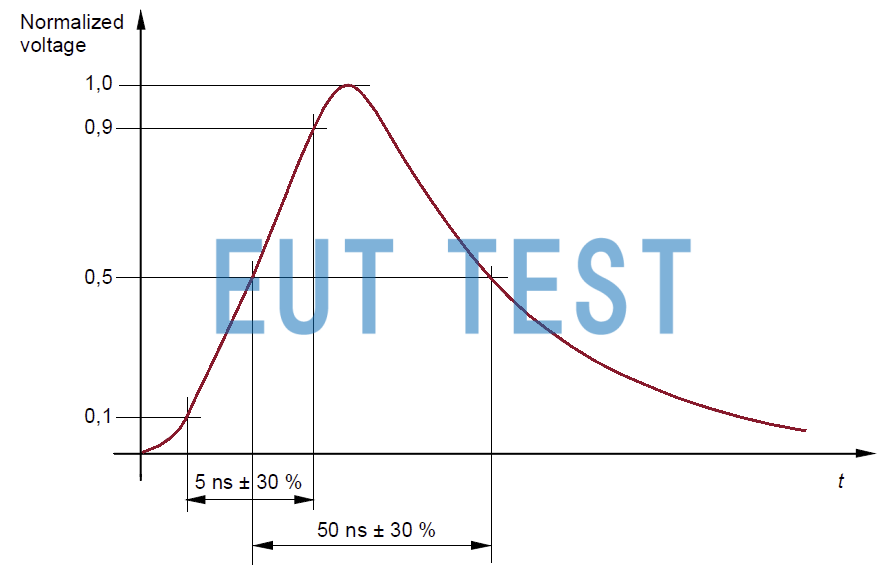

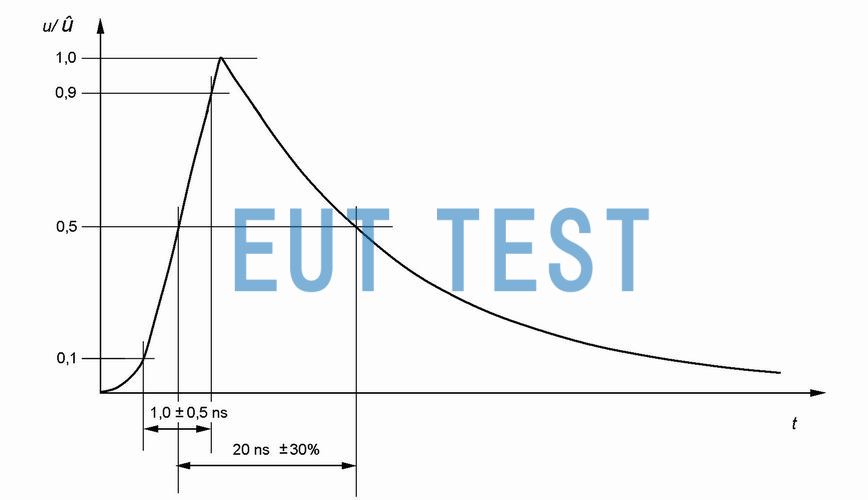

图 1符合 IEC 61000-4-4 的突发脉冲的时间曲线 |

|

源阻抗为 50 ohms 的脉冲从最小值为 ±2kV,前沿为 5 ns,后沿为 50 ns(半幅),应用于器件(图 1)。正是由这些脉冲组成了突发。

| IEC 61000-4-2 | 静电放电抗扰度测试 (ESD) |

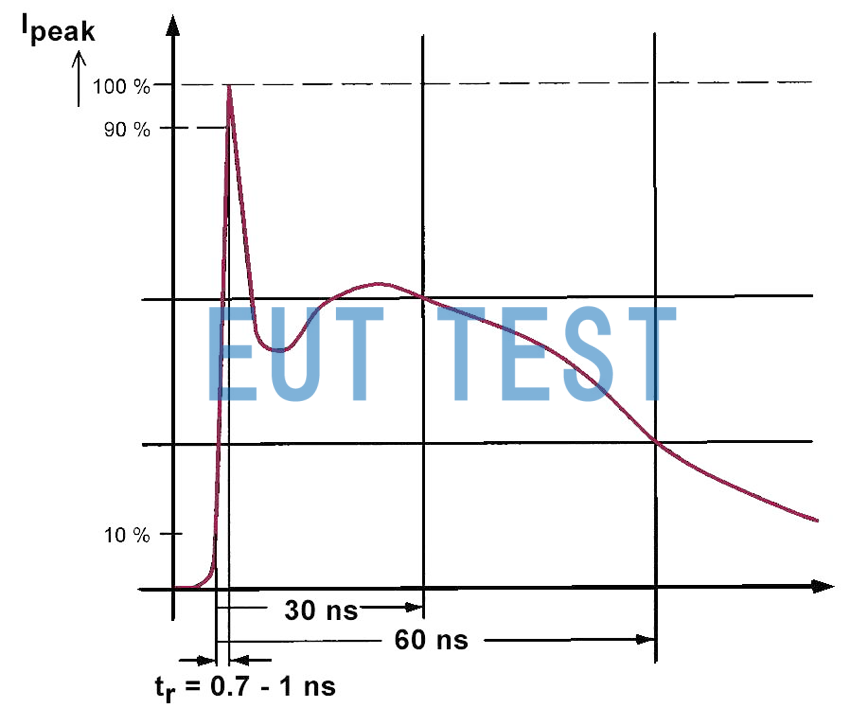

图 2符合 IEC 61000-4-2 的 ESD 脉冲时间曲线 |

|

源阻抗为 330 ohms 的脉冲至少为 ±6 kV,前沿为 0.7 ns,后沿为 5 ns(半幅)(图 2)

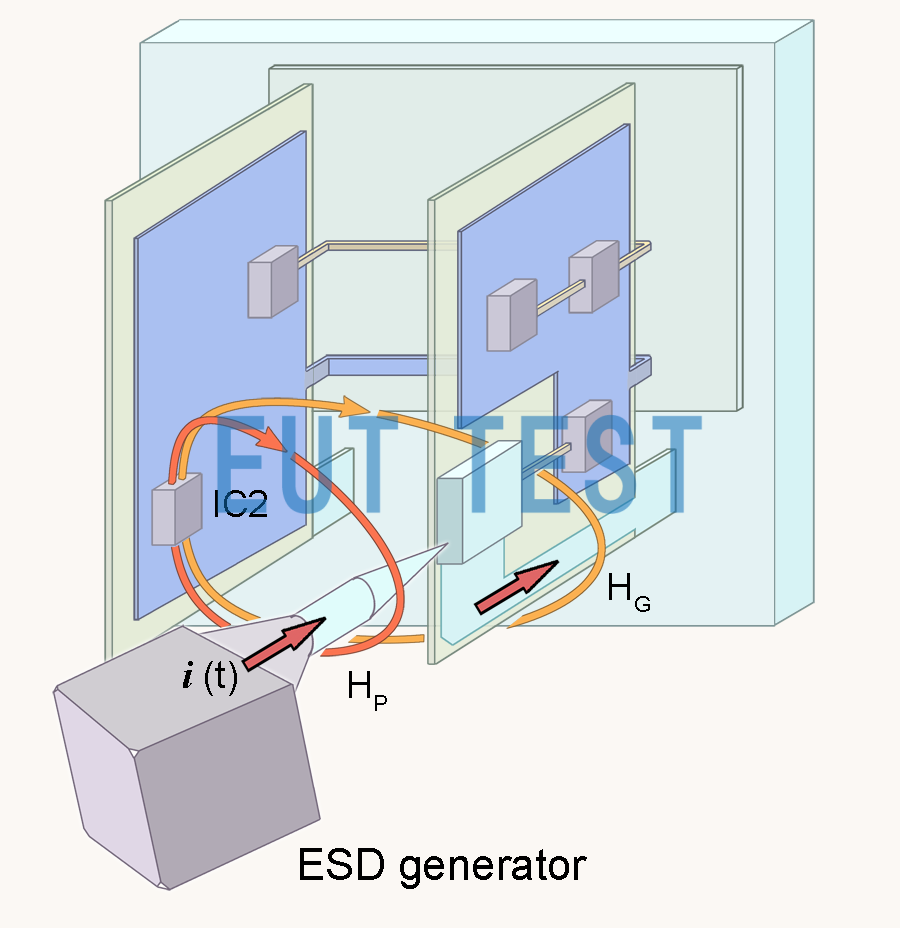

设备测试干扰的基本原理

为了证明它的抗扰度,脉冲形状的干扰被施加到设备的预期位置上,并且与预期位置无关。施加到器件上的电压 u(t) 的初级干扰脉冲(ESD 或突发)会导致脉冲干扰电流 i(t) 流过器件(图 3)。两种基本机制——磁耦合和电场(E场)耦合——虽然同时发生,但应单独考虑。

1. 磁场(感应)耦合

磁场干扰 H(t) 在携带干扰电流 i(t) 的导体周围形成。初级电路的阻抗越低,电流越大,因此磁场越高。

在理想情况下,直导体的场强由下式给出:

| [1] |  |

磁场干扰会穿透设备和周围的组件和印刷电路板。导体回路位于印刷电路板上或元件中(例如:IC,图 3)。磁场干扰通过电感器 L 感应出次级干扰电压 u_sec(t)。

| [2] |  |

例如,这种干扰电压可能存在于 IC pic 上或 IC 中,这可能会导致 IC 发生故障。

图3 电气设备中磁场耦合的机制

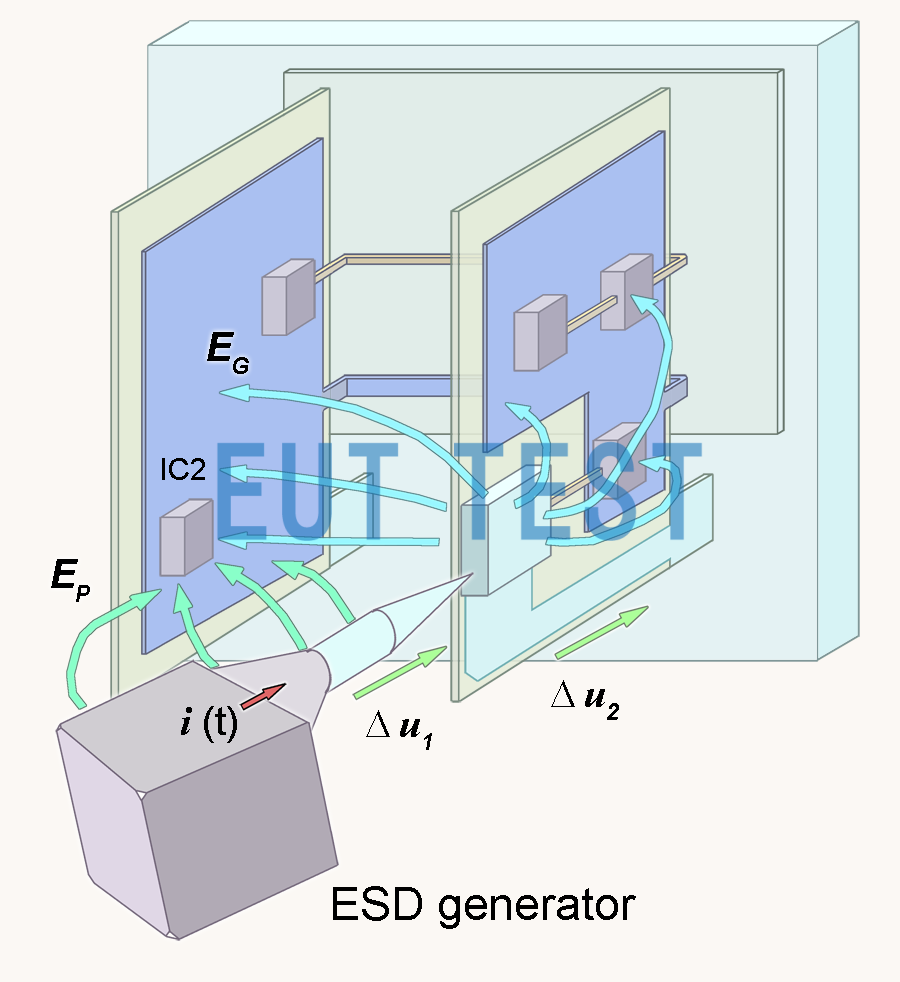

2. 电场耦合

施加到器件上的电压 u(t) 的主要干扰脉冲(ESD 或突发)会导致整个组件的电压降(图 4))。电场 E(t) 是从沿观察几何形状的电压差获得的。初级电流路径的阻抗越高,电压差就越大,因此产生的电场就越高。电场通过电容耦合将干扰作为位移电流 i(t) 传输到次级回路中,例如 [at] 信号电缆和/或 IC 引脚。该过程可以通过在 fF 范围内的耦合电容 C 来实现,如下文 [3] 中所述。电容耦合电流 i(t) 在次级回路的内阻处产生干扰电压。该干扰电压可能出现在 IC 引脚上并触发 IC 中的干扰。

| [3] |  |

图 4电气设备中电场耦合的机制

在这两种情况下(由磁场或 E 场引起的耦合),在从初级干扰电路到次级回路的过渡期间,干扰减少了一个因子(设备因子),并且位于有源电子设备(例如,在 IC 上)。通常在 ESD 器件测试期间出现的 6kV 干扰电压降低到 …0.1 V 到数百 V 的范围。这种降低取决于初级和次级干扰电路中的阻抗。

安装在印刷电路板上的 IC 暴露于干扰驱动的磁场 H(t) 和 E 场 E(t)。

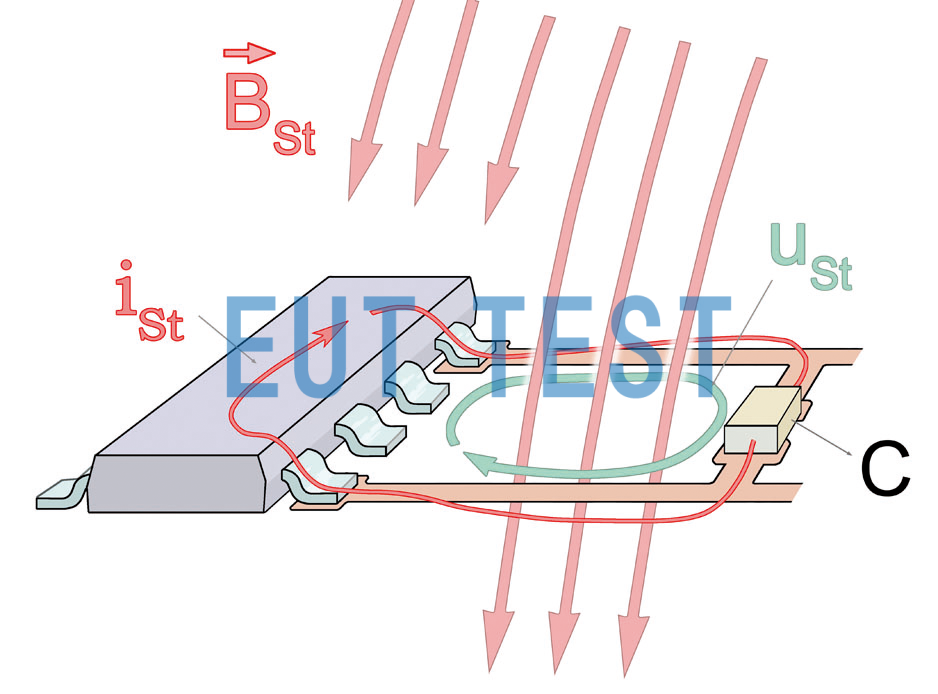

磁场(感应)耦合到 IC

磁通密度 B st (t) 穿过最小的导体回路(例如,在 IC 和连接的去耦电容器之间,图 5)。如[4] 和 [5] 中所述,磁通量 Φ 在电路回路中感应出电压 U st。

| [4] |

| [5] |  |

电压 U st驱动干扰电流进入 IC。由于在导体回路中形成,该干扰源的阻抗很低。这会导致高电流I st (t)。

图 5通过磁场耦合到 IC 的模型

电场(电容)耦合到 IC

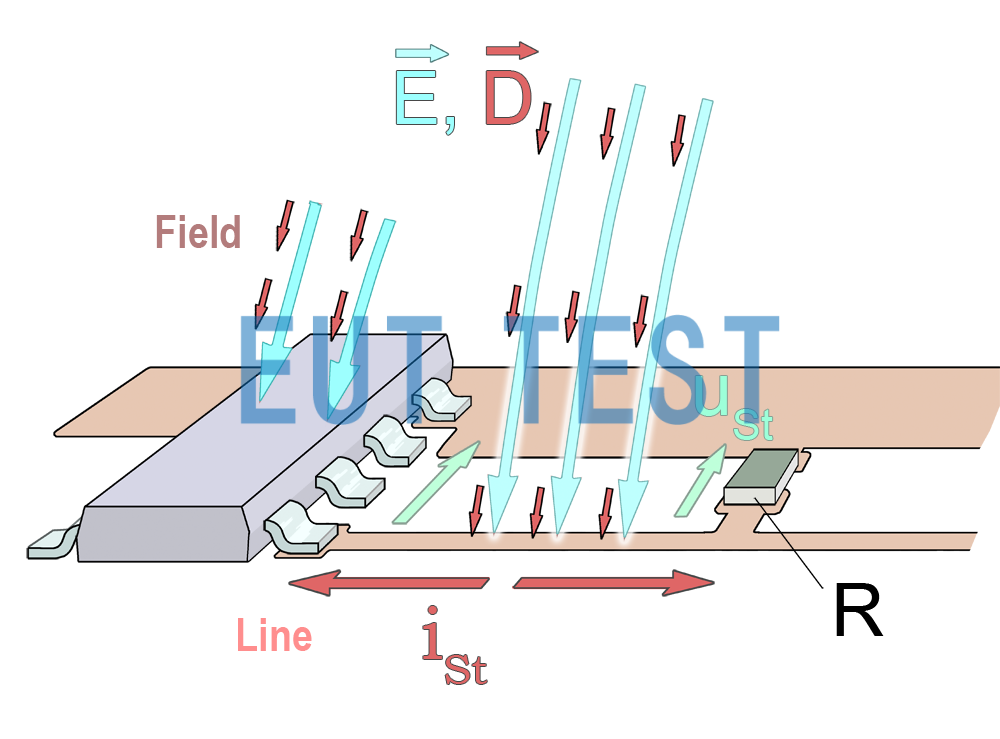

电场强度 E(t) 或与导电表面相关的位移电流 D(t) 会在导体中产生干扰 I st (t)(图 6)。这种干扰会导致导电表面上的电压升高 U st (t)。这种电压升高会使通过走线传输的逻辑信号失真。位移电流 I st (t) 也可以合并到 IC 中并触发进一步的干扰事件。“电场”干扰源具有高阻抗。

图 6通过 E 场耦合到 IC 的模型

模拟

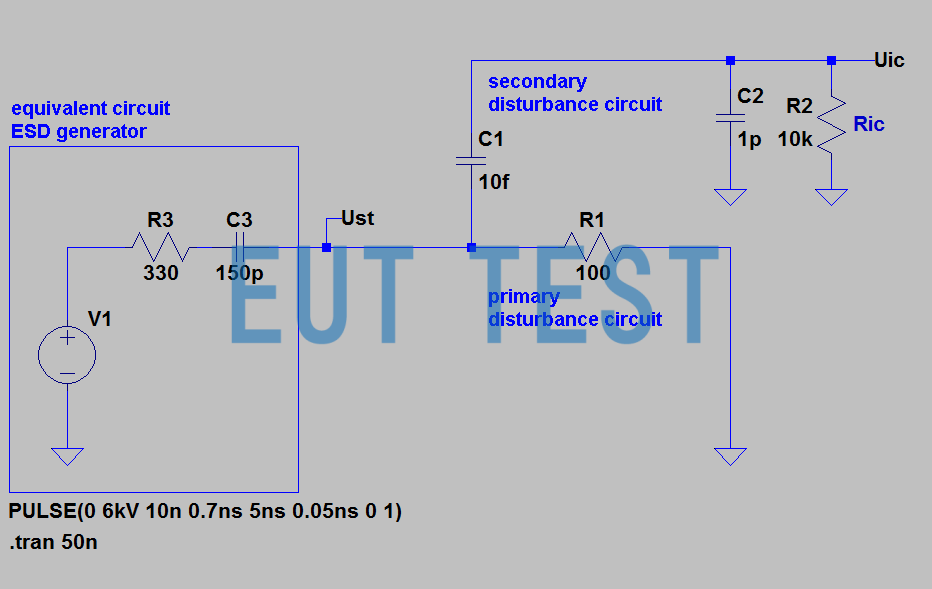

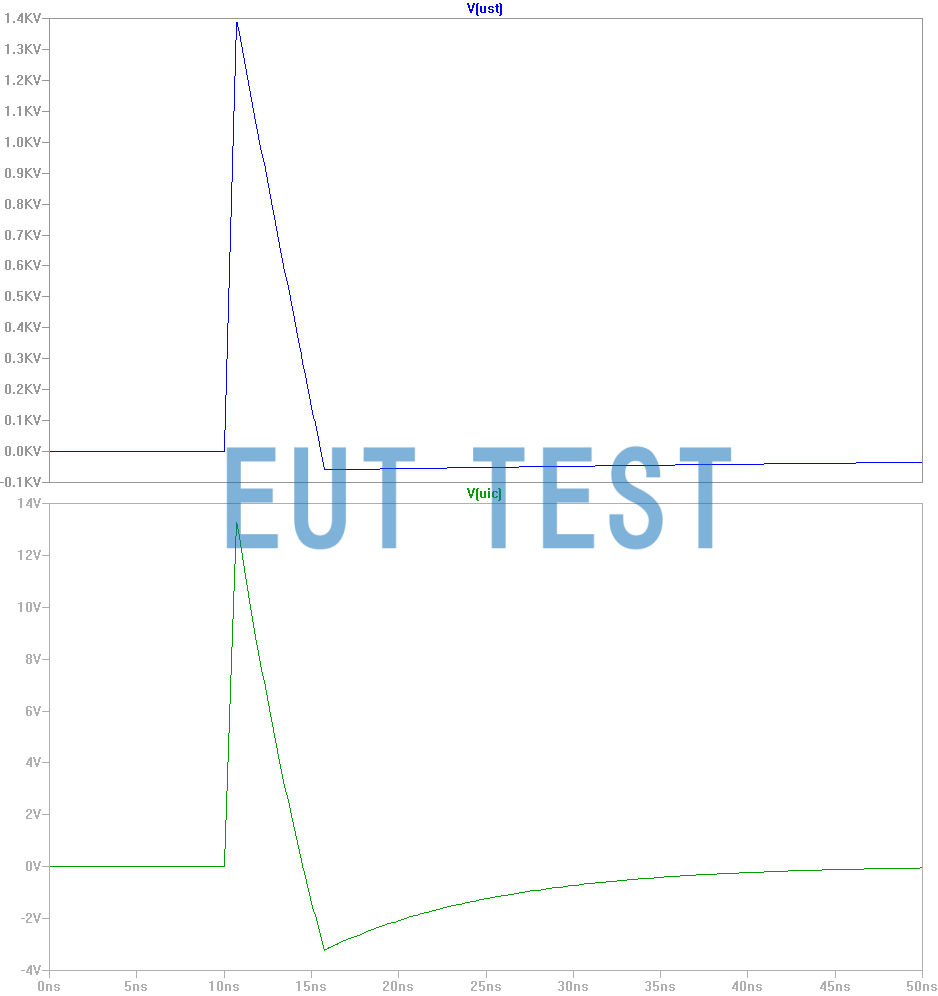

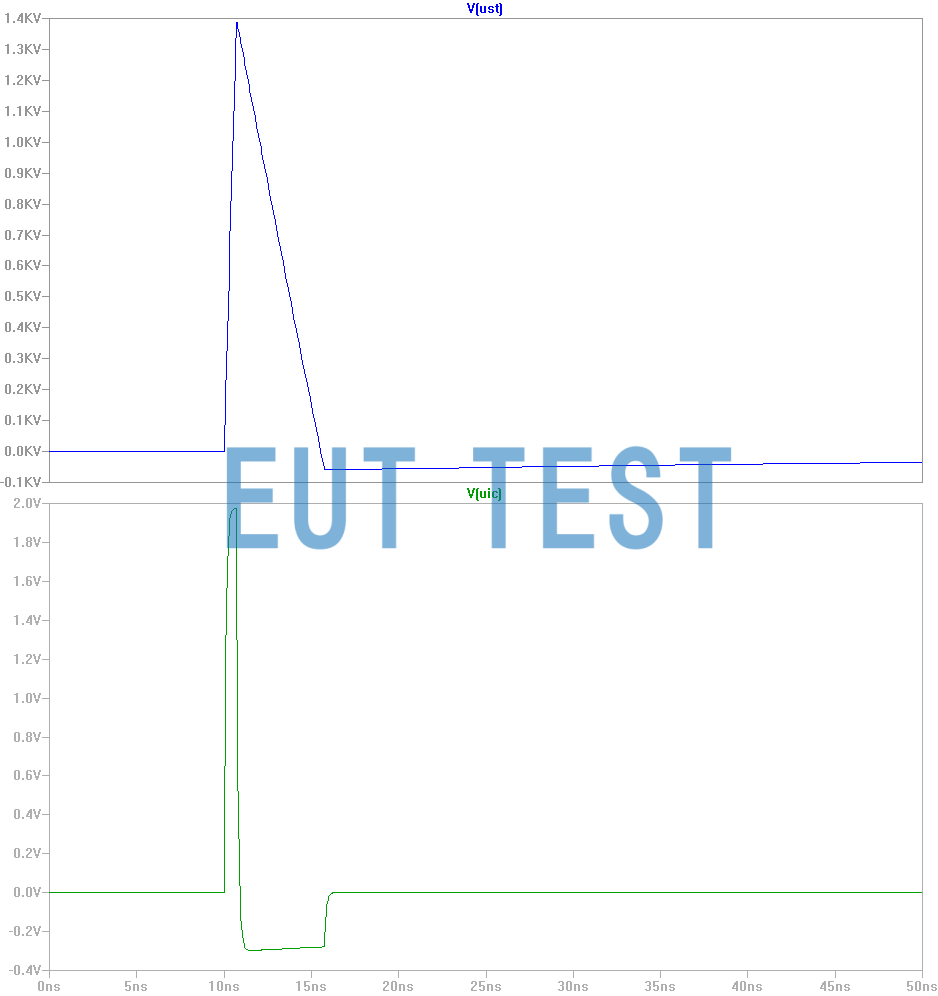

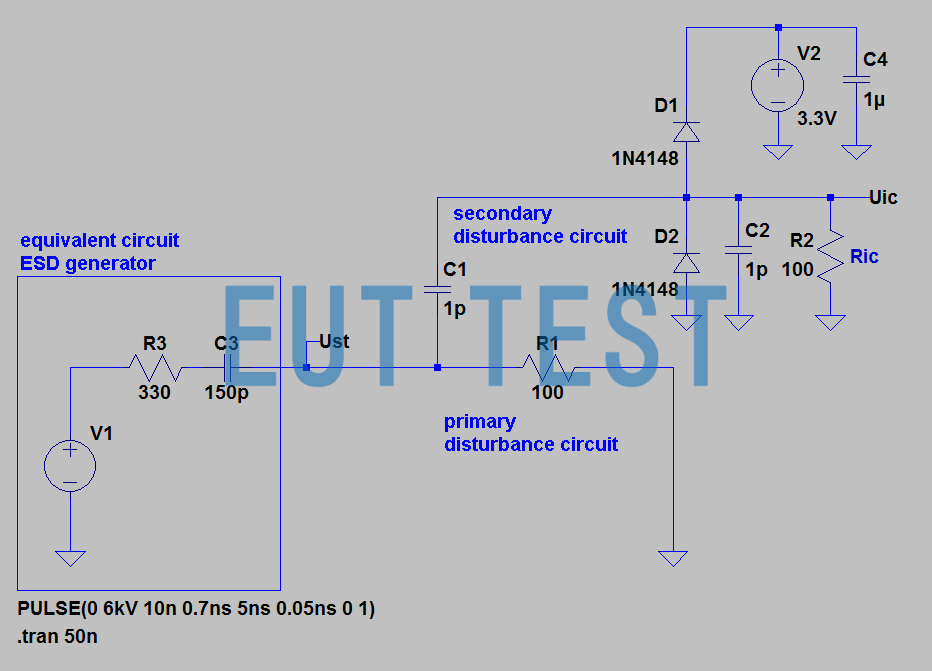

以下模拟(图 7-12)展示了一般情况。在图 7中,ESD 脉冲的生成已大大简化。等效电路基于图 4中所示的电容耦合原理。

估算 IC 上的干扰电压

幅度为 6kV 的正干扰脉冲作为接触放电注入初级干扰电路(图 7)。1.4 kV的干扰电压峰值 (U st ) 源自初级阻抗 R1(图 4)。13.5 V 干扰电压通过跨 C1 的电容耦合(电场耦合)与高阻抗 IC 引脚保持接触。初级干扰电路的阻抗可能会大很多(1kOhm),使得IC引脚的干扰电压可以超过100V。这允许显着超过 IC 的最大额定值规格。

图 7 耦合电干扰场时估算 IC 引脚上的干扰电压的示例

图8 一、二次回路耦合干扰电压曲线及峰值

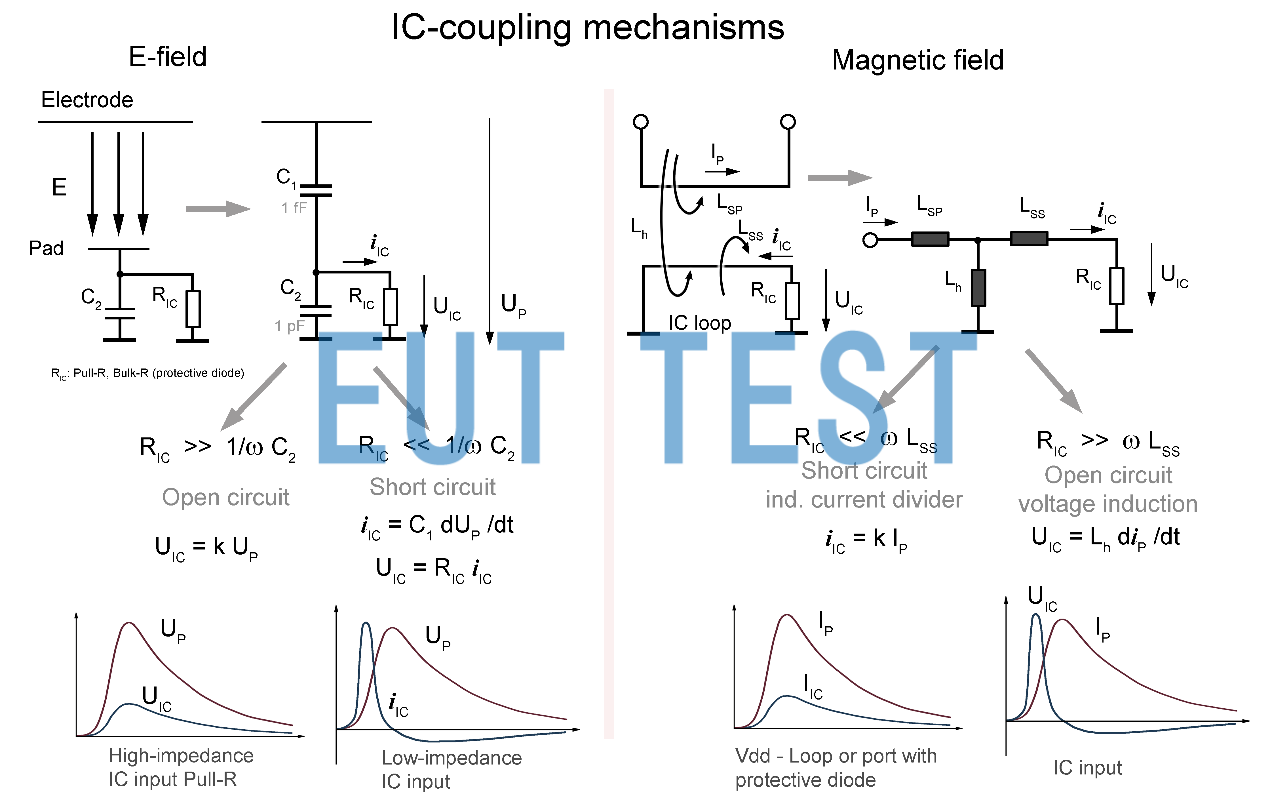

耦合方式

耦合类型还取决于源阻抗与负载阻抗的比率,即与 IC 的输入阻抗之比。

电场(电容)耦合

斜率为 1 ns,传输最大速率为 1 GHz。假设耦合电容 C1 为 1 pF。耦合电容的阻抗 X 为 159 欧姆。当IC的输入电阻为10k时,输入电阻远大于源电阻(C1的阻抗)。因此,R2 处(IC 处)的相邻干扰脉冲具有与主干扰脉冲相同的波形。这导致与电容分压器 C1、C2 的比例分压。

IC 的 Ri ≫ X C1

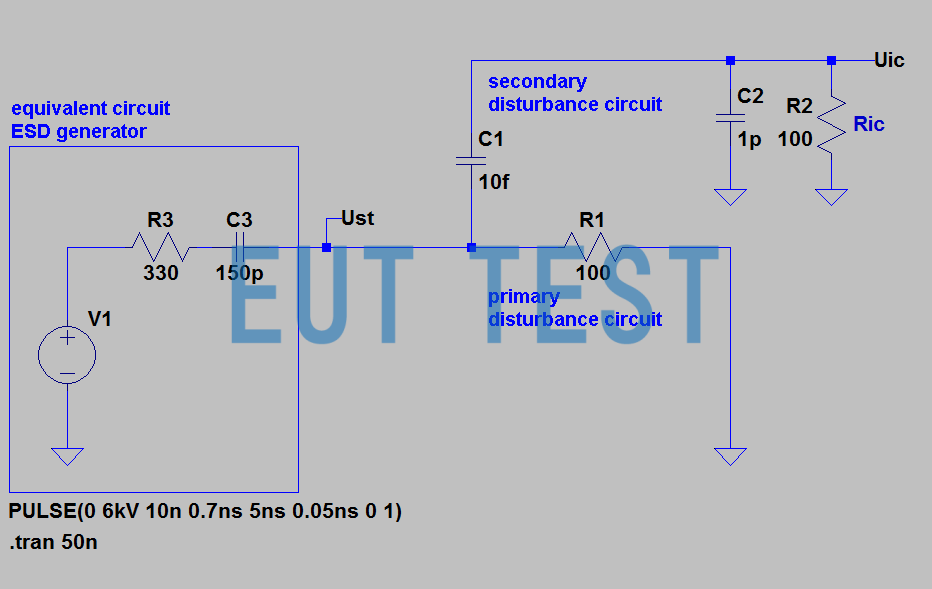

当负载阻抗小于源阻抗时,将获得完全不同的条件。以下示例假设 R2 = 100,C1 = 10fF。

IC 的 Ri < X C1

在这些条件下,主要干扰脉冲在 IC 处被区分(图 9和10)。

图9 干扰耦合通过电场的微分效应的等效电路

图10 电场干扰耦合的微分效应曲线

磁场(磁)耦合

对于 H 场耦合,条件相反。在空闲状态下,

R ic ≫ X ss 是微分的,

R ic < X ss是分流的。

耦合机制的总结如图 11所示。在磁场耦合中,假设变压器等效电路图具有主电感 (L h ) 和漏电感 (L s )。

图 11 IC 耦合机制的工作区域:电流-电压-分压/微分

从器件到芯片的EMC测试分析-第 2 部分

集成电路效果

保护机制已集成到 IC 中,以防止浪涌对其敏感结构造成破坏。

由于这些现有保护系统的设计方式,假设要保护的 IC 不由电源电压供电,即它不工作。因此,IC 受到保护,免受高静电电压的影响,这可能会导致发生在电子设备的制造、运输和加工过程中。

与现有 IC 保护系统的设计相比,上述器件测试中的 IC 由电源电压供电,因此处于运行状态。

在实际操作过程中(IC 供电)的干扰下,保护电路可能会在不经意间造成内部短路。

集成到 IC 中的保护机制通常不会由制造商公开。但是,可以假设以下机制:

- 电源连接处的电涌受功能上与 Z 二极管对应的结构的限制。

- 输入和输出的过压受二极管或晶体管结构的限制。

负载阻抗取决于要测试的 IC 引脚。电源连接的特点是低负载阻抗。在这些连接处,电容耦合信号如上所述被微分。如果信号是电感耦合的,电压将分裂。当保护电路的限制电压保持在规定的电平范围内时,IC 输入端的阻抗会相对较高。如果超出此范围,电容桥接电源系统将导致保护电路和电源的阻抗急剧降低。

这导致分压行为和保护元件的电压限制效果的差异的组合。当干扰电流通过保护电路流入IC时,会触发内部功能错误。

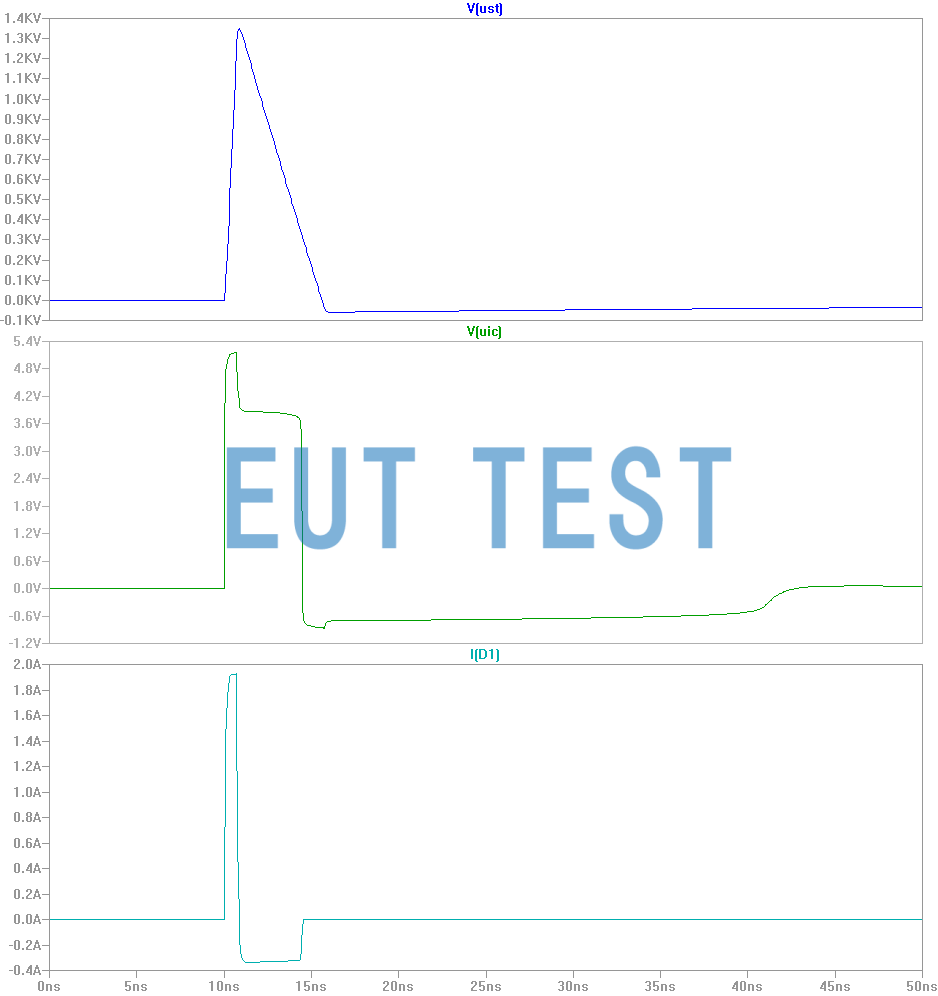

图 1 带有集成 IC 输入的 ESD 枪的简化等效电路。带保护二极管的输入

图 2 图 1 的干扰电压曲线

图 2图 1 的干扰电压曲线

根据二极管的特性,会出现不同的曲线轨迹。图 1和图2中使用了慢速 Si 二极管。

通过二极管流入供电系统的显着干扰电流 I(D1) 是显而易见的。这可以在图2中看到。重要的是要考虑到这种情况不仅发生在器件测试期间(根据 IEC 61000-4-2),而且在发生静电放电的 IC 正常应用期间也会发生。

IC 测试所需的脉冲宽度

定义用于 IC 抗扰度测试的测试脉冲的目的是能够以广泛的结构宽度重复测试 IC。这是因为 IC 的内部处理速度取决于其结构宽度。例如,粗结构 IC 对干扰事件具有一定的惯性。

动态开关阈值/干扰阈值可作为评估 IC 的基础。

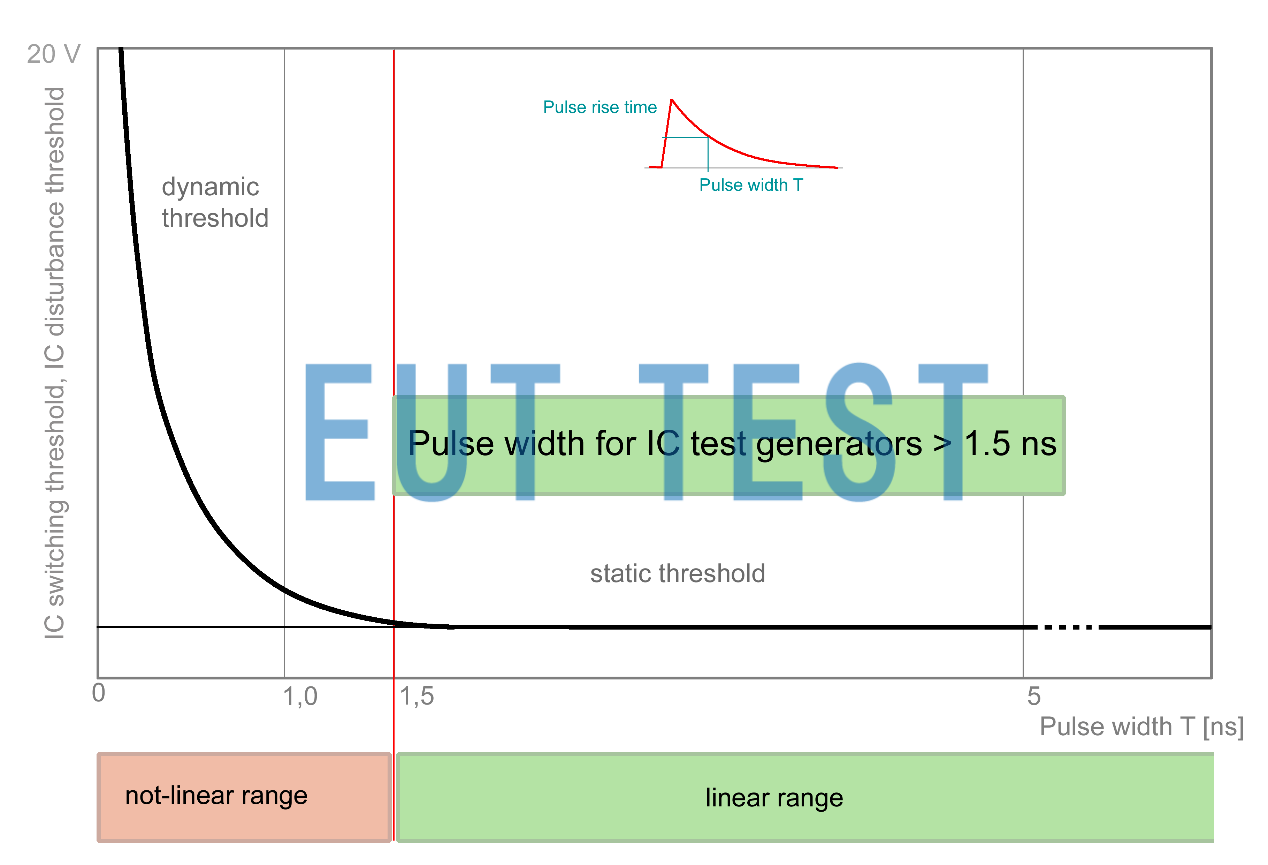

图 3显示了 X 轴上的扰动脉冲的脉宽 T 和 Y 轴上的扰动阈值。对于宽脉冲(图 3,> 1.5 ns),干扰阈值接近恒定(静态干扰阈值)。对于短脉冲(图 3, < 1.5 ns),干扰阈值增加,IC 变得不敏感(动态干扰阈值)。静态/动态转换的边界取决于 IC 的结构宽度。

在电源系统干扰的情况下,应考虑额外的行为模式。如在确定图3中,用于测试集成电路的测试发生器的脉冲宽度必须> 1.5纳秒。由于推动更好更快的技术,这个限制是可变的,允许脉冲宽度 < 1.5 ns 的更快 IC。

图 3 描述 IC 的静态和动态干扰阈值

为了获得可重复的结果,必须在线性范围内(即在静态干扰干扰阈值范围内)选择 IC 测试的脉冲宽度。

20 年前,干扰脉冲为 2 ns 的 IC 无法受到干扰。随着技术的进步,结构宽度减小,从静态到动态范围的转变向更短的脉冲宽度转变。

因此,今天静态范围内的测试脉冲也可用于更快和未来技术的 IC。

然而,相反,必须注意的是,结构更小、电源电压更低的 IC 具有更低的干扰阈值和更高的灵敏度。因此,抗扰度测试的重要性在未来只会增加。

IC测试方法

根据初步考虑,应具备低阻抗和高阻抗的脉冲源。应考虑以下因素:替换电路、边缘陡度和最大电压电平。

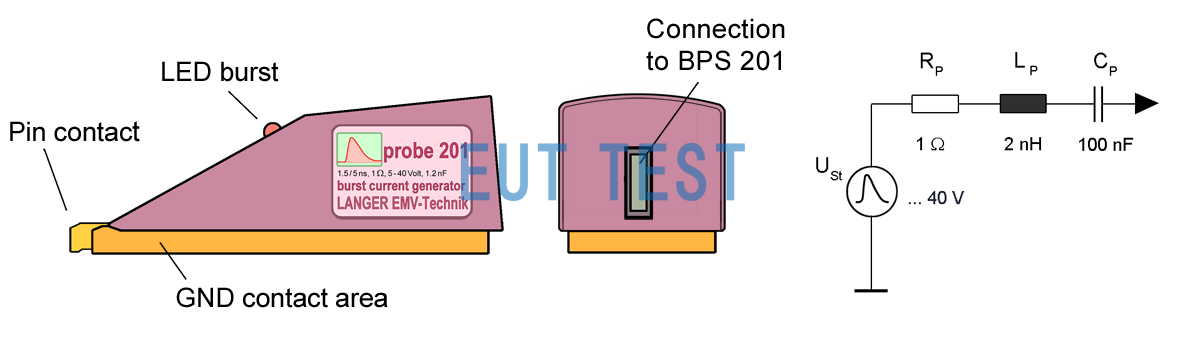

低阻抗脉冲源 (Probe P2xx) 用于测试电源连接。为此,从要测试的电路中移除支持电容器。它被位于探头中的 C P电容器取代。Probe P2xx 的脉冲宽度由前沿和后沿形成,在静态干扰阈值范围内为 1.2 ns/3.5 ns。

低阻抗脉冲源(低阻抗探头 P2xx)

图 4低阻抗探头的结构和等效电路图

| R P = 1 欧姆 |

| L P ≤ 2 nH |

| Ç P ≥100 nF的 |

| 电压高达约。± 40 伏 |

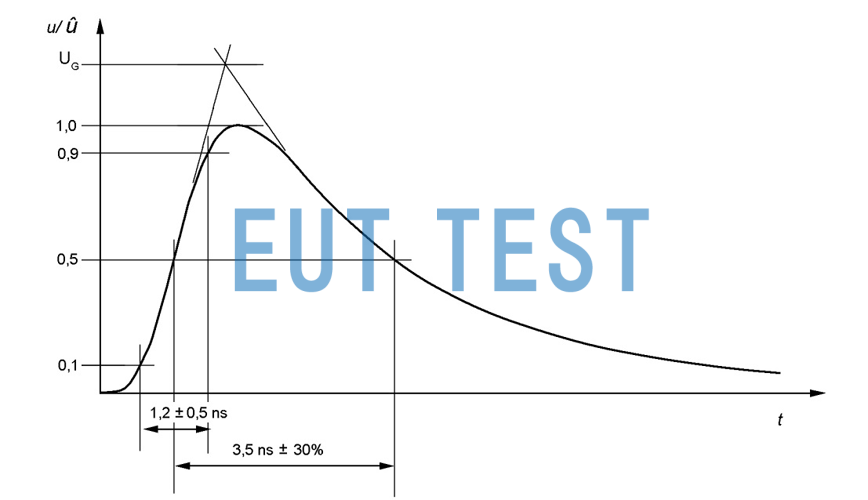

图 5低阻抗探头的曲线形状

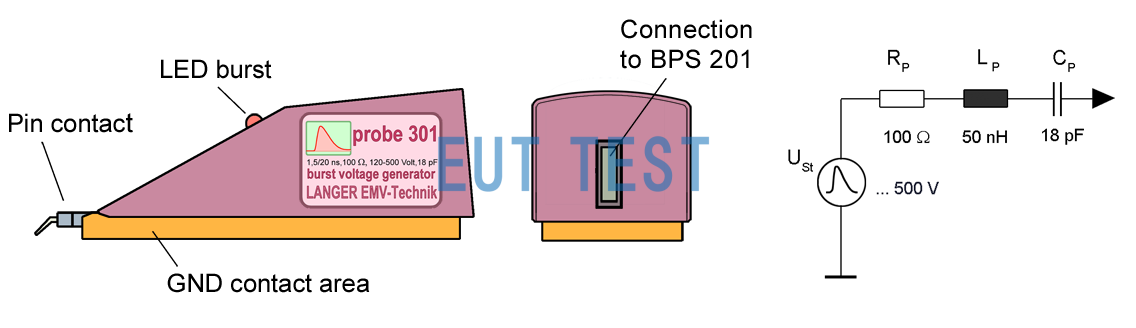

高阻抗脉冲源(高阻抗探头 P3xx)

图 6高阻抗探头的结构和等效电路

| R P = 100 欧姆 |

| L P ≤ 50 nH |

| Ç P = 18 pF的 |

| 电压高达约。± 500 伏 |

图 7高阻抗探头的曲线形状

Probe 3xx 的脉冲宽度由前沿和后沿形成,在静态干扰阈值范围内为 1 ns/20 ns。如果发生短路,Probe P3xx 的脉冲宽度会降低到 2 ns。当保护电路导通以在静态干扰阈值范围内重新建立脉冲宽度时,就会发生这种情况。内部瞬态过程进一步扩大了干扰脉冲。

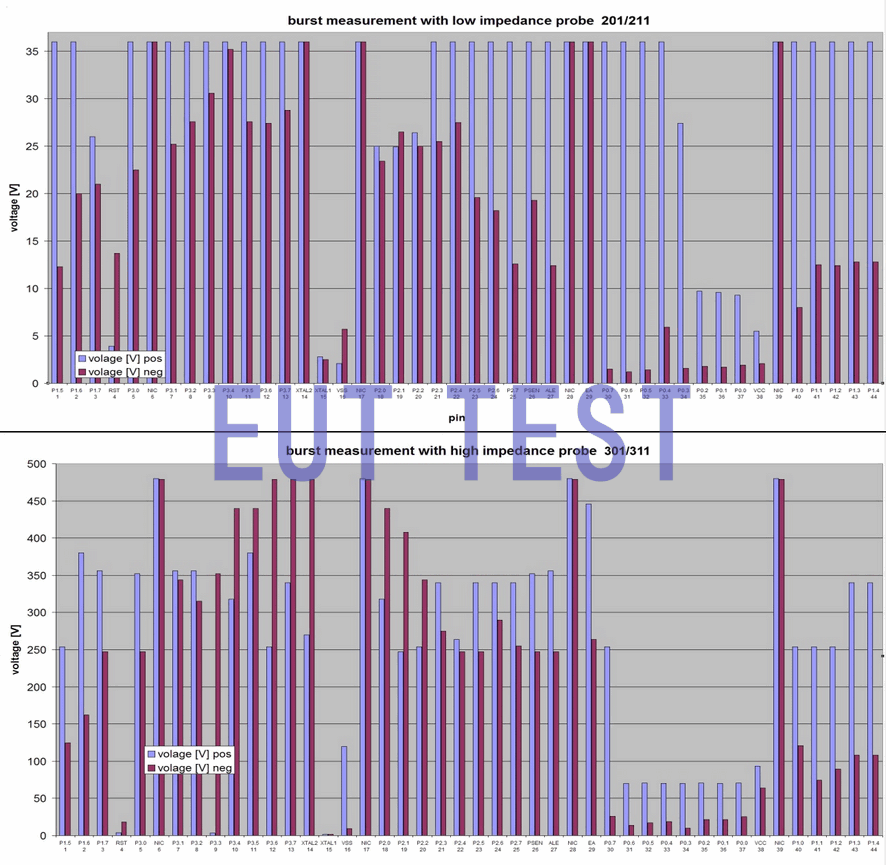

图 8在粒度级别上显示了 IC 的引脚干扰阈值。

通过一些比较经验,可以识别出特别脆弱的引脚。裸露的引脚应能承受 > ±15 V 的低阻抗源干扰阈值和 > ±150 V 的高阻抗源干扰阈值。

图 8 8051 IC 引脚粒度干扰阈值

图 8 8051 IC 引脚粒度干扰阈值

使用 IC 测试脉冲进行仿真

为了评估所描述的测试脉冲的影响,可以使用测试脉冲仿真模型。

这有助于 IC 或 ASIC 的制造商预测所建议的测试方法的结果。值得注意的是干扰期间 IC 内部发生的情况;哪些电路受到影响以及如何受到影响。内部寄生元件,例如线路电感和寄生电容,以及只有 IC 制造商知道的实际保护结构,起着至关重要的作用。

除了信号失真外,内部供电系统的干扰在故障分析中也起着决定性的作用。外部信号失真一般可以通过电报重复、纠错等设计措施来控制。但是,如果干扰事件导致部分内部电源崩溃或振荡,则无法控制它们。这会影响 IC 的整体功能。

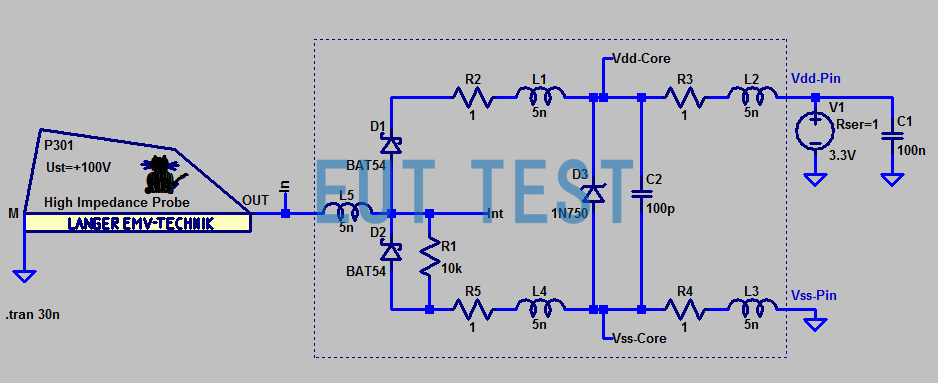

在图 9高阻抗探头 P301 的 LTSpice 模型连接到简化的 IC 等效电路的输入。输入由保护二极管 D1 和 D2 组成,它们连接到 IC 的 Vdd 和 Vss 系统。等效电容 C2 (100pF) 代表 IC 的核心。最重要的电路元件由 L1-L4、R1-R5 和 D1-D3 实现。电源钳位 D3 可保护磁芯免受浪涌影响。

图 9 简化 IC 等效电路输入端的高阻抗探头 P301 的 LTSpice 模型

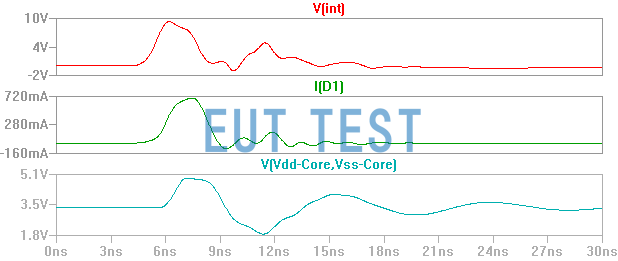

图 10 使用高阻抗探头 P301 进行 LTSpice 模拟的曲线形状

对于 +100 V 的测试电压,IC 中会产生干扰电压 V(int)。电流 I(D1) 流过保护二极管 D1。当前重新加载核心容量。在 IC 内部,电源系统 V(Vdd-Core, Vss-Core) 上会发生瞬态响应(图 10)。在这种情况下,内核电压从 3.3 V 下降到 1.8 V,并可能导致 IC 发生故障。

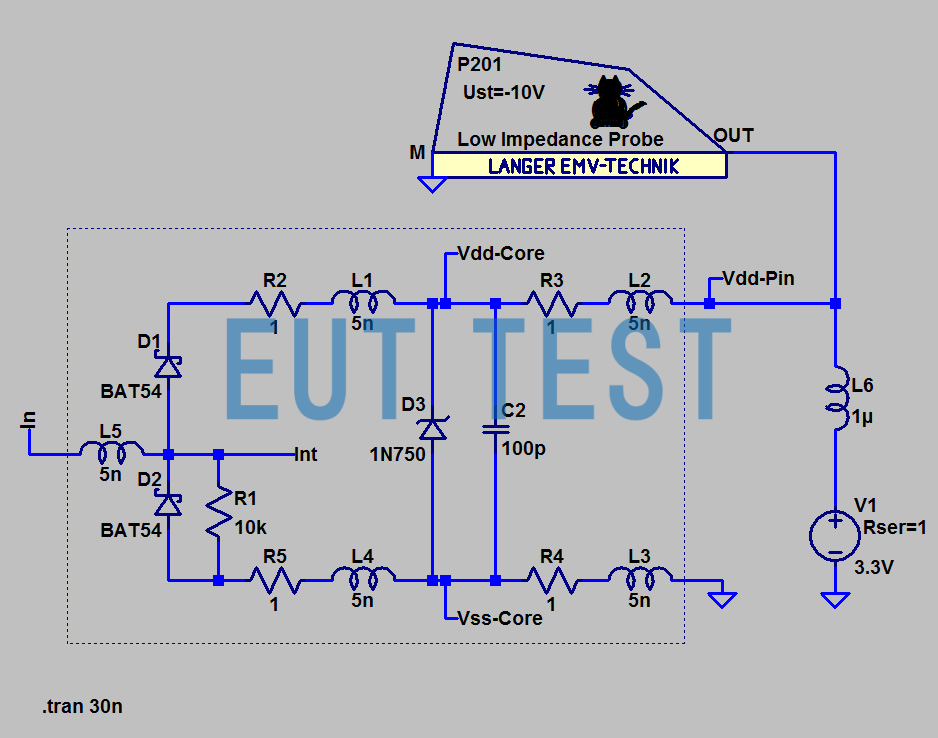

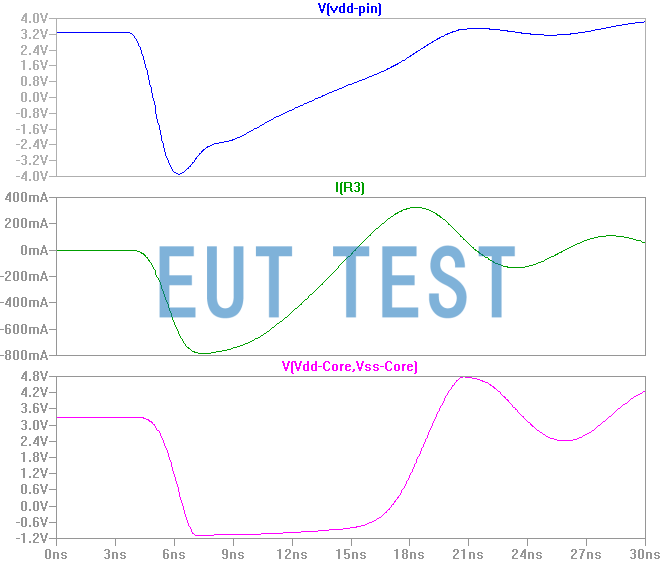

在图 11 中,低阻抗 Probe P201 的 LTSpice 模型连接到 IC 等效电路的 Vdd 引脚。备用电容器 C1 已被移除并替换为探头 P210。已在探头 P201 中设置了 -10 V 的电压。干扰会在 Vdd 引脚上产生 -4 V 的压降(图 12)。干扰电流主要通过电源钳位D3和核心电容C2流向Vss。发生这种情况时,内核电压 V(Vdd-Core, Vss-Core) 下降到 -1.2 V。这肯定会干扰 IC 的功能。

图 11 简化 IC 等效电路输入端的低阻抗探头 P201 的 LTSpice 模型

图 12 使用低阻抗探头 P301 进行 LTSpice 模拟的曲线形状

图11和12所示的现象只是示例性地说明了IC的工艺。因此,展示了一种用于理解 IC 中高度复杂干扰的解决问题的方法。

通过将 LTSpice 仿真和测试与真实 IC 和探针(P201 和 P301)相结合,可以使用高效的开发工具来研究和改进 IC 的 EMC 特性。测试发生器的 LTSpice 模型使 IC 制造商更容易使用所描述的测试程序。将来,人们应该能够在 IC 开发之初指定 EMC 属性。

- 创建日期: 2024-08-26 10:25:20 ;

- 最后修改日期: 2024-08-26 18:25:20 ;